The ESP Vision

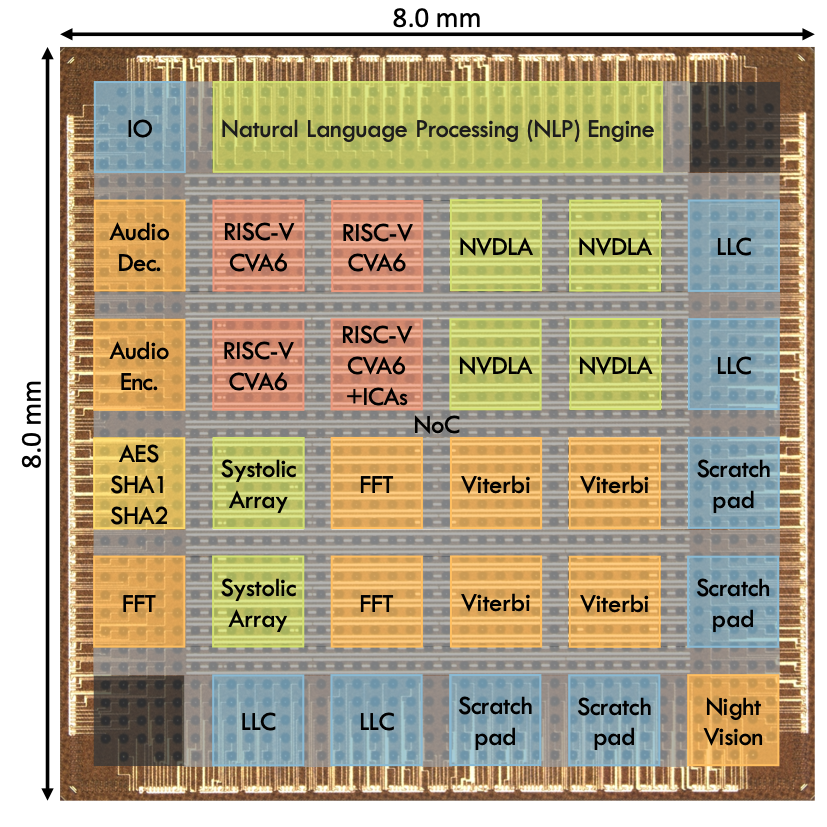

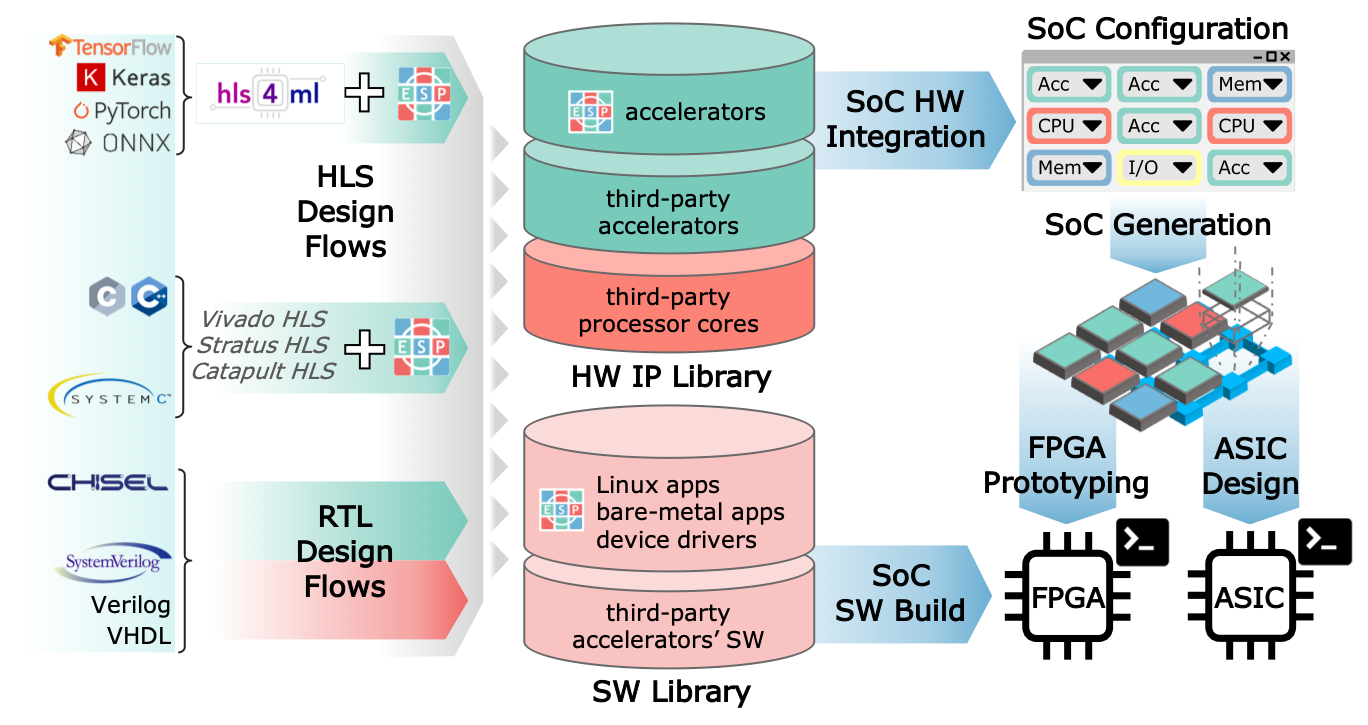

ESP is an open-source research platform for heterogeneous system-on-chip design that combines a scalable tile-based architecture and a flexible system-level design methodology.

ESP provides three accelerator flows: RTL, high-level synthesis (HLS), machine learning frameworks. All three design flows converge to the ESP automated SoC integration flow that generates the necessary hardware and software interfaces to rapidly enable full-system prototyping on FPGA.

Overview

- Architecture

- Accelerator design and integration flows

- SoC design flow

- Mix & match SoC floorplanning GUI

- Automatic SoC generation

- Full-system RTL simulation

- Rapid FPGA prototyping

- Software support

- Bare-metal

- Linux SMP

- FPGA development boards

- Xilinx Virtex UltraScale+ FPGA VCU118 and VCU128

- Xilinx Virtex-7 FPGA VC707

- proFPGA Virtex7 XC7V2000T FPGA

- proFPGA Virtex Ultrascale XCVU440 FPGA

For more information check out the documentation section!

See here some of the supported projects, tools and languages:

Publications

Overview paper:

Agile SoC Development with Open ESP

Paolo Mantovani, Davide Giri, Giuseppe Di Guglielmo, Luca Piccolboni, Joseph Zuckerman, Emilio G. Cota, Michele Petracca, Christian Pilato, Luca P. Carloni

(Invited) IEEE/ACM International Conference On Computer Aided Design (ICCAD), 2020

The Publications page contains the complete list of publications related to ESP.

What’s new

- Docker image for ESP

- Instructions in the setup guide

- Accelerator design flow in C/C++ with Catapult HLS

-

Integration of the 32-bit Ibex processor

-

Multi-processor support for the RISC-V Ariane cores

- Accelerator design flow in SystemC with Catapult HLS

Coming soon

-

Dynamic partial reconfiguration of accelerator tiles

-

ASIC design flow

-

New accelerators for machine learning, cryptography, and more