Guide – How to: design a multi-core SoC

Latest update: 2023-02-23

This guide illustrates how to generate and test a multi-core ESP SoC. This tutorial has many steps in common with the “How to: design a single-core SoC” tutorial, which is referenced by this guide multiple times. Make sure to complete the prequisite tutorials before getting started with this one, as this guide builds on top of them without repeating content.

- Target FPGA board

- SoC configuration

- Cache Configuration

- Debug link configuration

- FPGA prototyping

- FPGA prototyping with prebuilt material

Note: The users have access to prebuilt material to run the tutorial on an FPGA, without executing all the previous steps. See the ‘FPGA prototyping with prebuilt material’ section at the end of this guide.

Target FPGA board

For this tutorial we target the Xilinx VC707 evaluation board. Move to the proper working folder:

# Move to the Xilinx VC707 working folder

cd <esp>/socs/xilinx-vc707-xc7vx485t

SoC configuration

Open the ESP configuration GUI:

make esp-xconfig

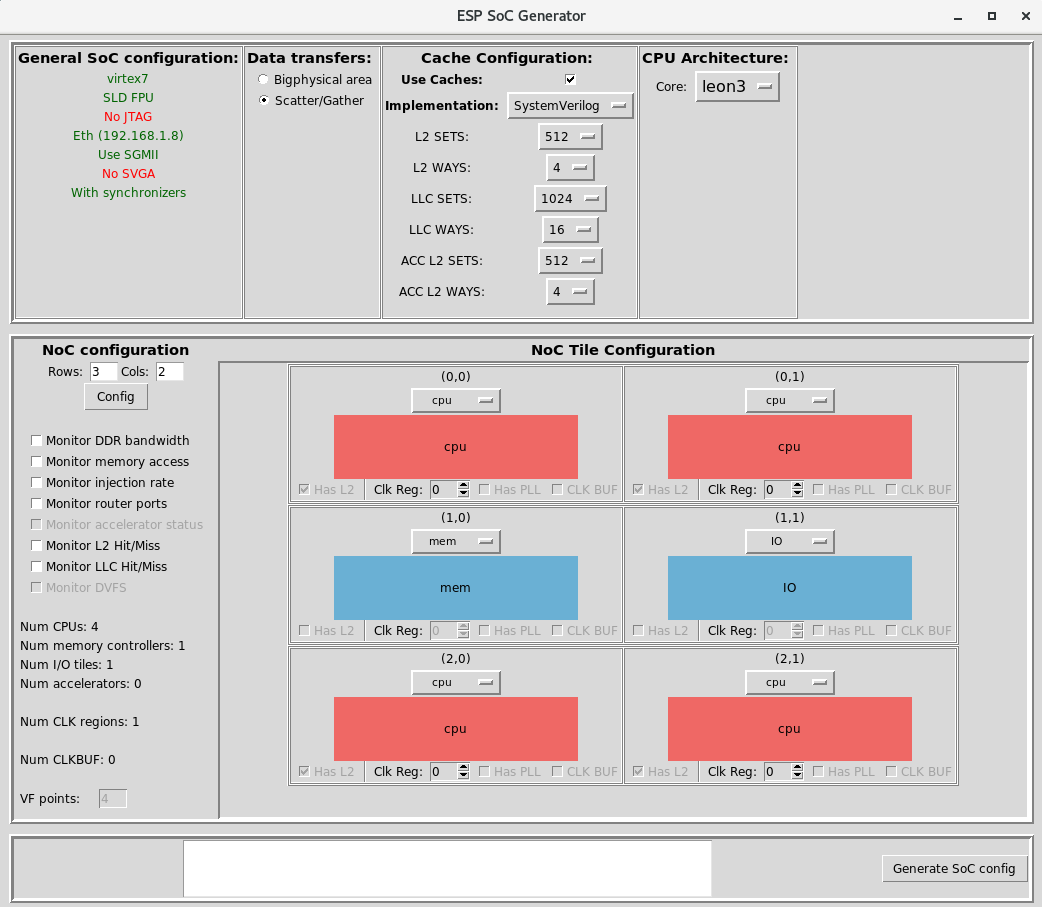

Select a 3x2 or 2x3 layout and set 4 processor tiles, 1 memory tile and 1

I/O tile, then save and close. The figure below shows the GUI with a possible

configuration for a quad-core ESP instance. Make sure the ESP caches are

enabled, because they are mandatory for multi-core instances of ESP. To support

multi-core operation the ESP caches implement a directory-based MESI protocol

over the NoC.

Note: Make sure to select the Leon3 processor, because multi-core is not supported for the Ariane core yet. The multi-core for ESP with Ariane is under development.

Cache Configuration

The ESP Cache hierarchy is mandatory for a multi-core SoC. See the section “ESP Cache Hierarchy” from the “How to: design a single-core SoC” guide for more details.

Debug link configuration

Follow the “Debug link configuration” instructions from the “How to: design a single-core SoC” guide.

FPGA prototyping

Follow the “FPGA prototyping” instructions from the “How to: design a

single-core SoC” guide. The only

difference is that before compiling Linux with the make linux command, you

should enable the Linux multi-core (Linux SMP) by setting a flag in the local

Makefile in the socs subfolder you’re working in.

SMP = 1

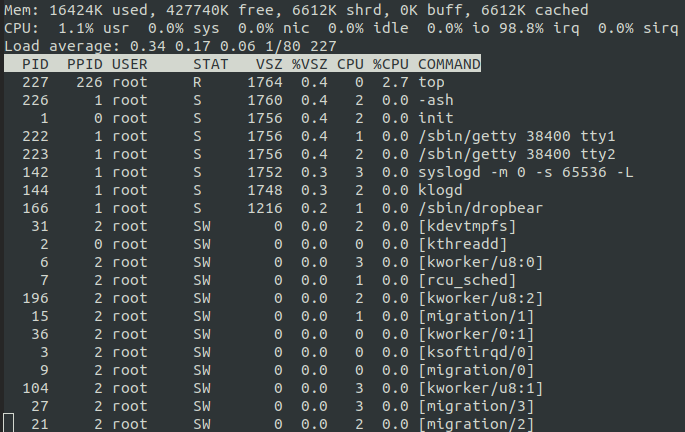

Once you login into Linux you can run top in the terminal to see that the

Linux processes are running on all four processor cores. See an example in the

image below:

FPGA prototyping with prebuilt material

Follow the “FPGA prototyping with prebuilt material” instructions from the “How to: design a single-core SoC” guide.