ASPLOS 2023 tutorial

Design of Heterogeneous SoCs for ASIC and FPGA Targets with ESP

Latest update: 2023-03-26

Logistics

Tutorial date: Sunday March 26, 2023.

Tutorial venue: Sheraton Vancouver Wall Centre - (Port Alberni (4th floor)) .

Tutorial registration: Registration instructions.

Preliminary setup: Instructions.

Hands-on tutorial steps: (COMING SOON!)

If you are interested in attending this tutorial, please be sure to sign up for it when registering for ASPLOS.

What is ESP?

The system-on-chip (SoC) lies at the core of modern computing systems for a variety of domains, from embedded systems to data centers. In any given domain, the success of a particular SoC architecture is bound to the set of special-purpose hardware accelerators that it features next to general-purpose processors. This heterogeneity of SoC components brings new challenges to hardware designers as well as software programmers.

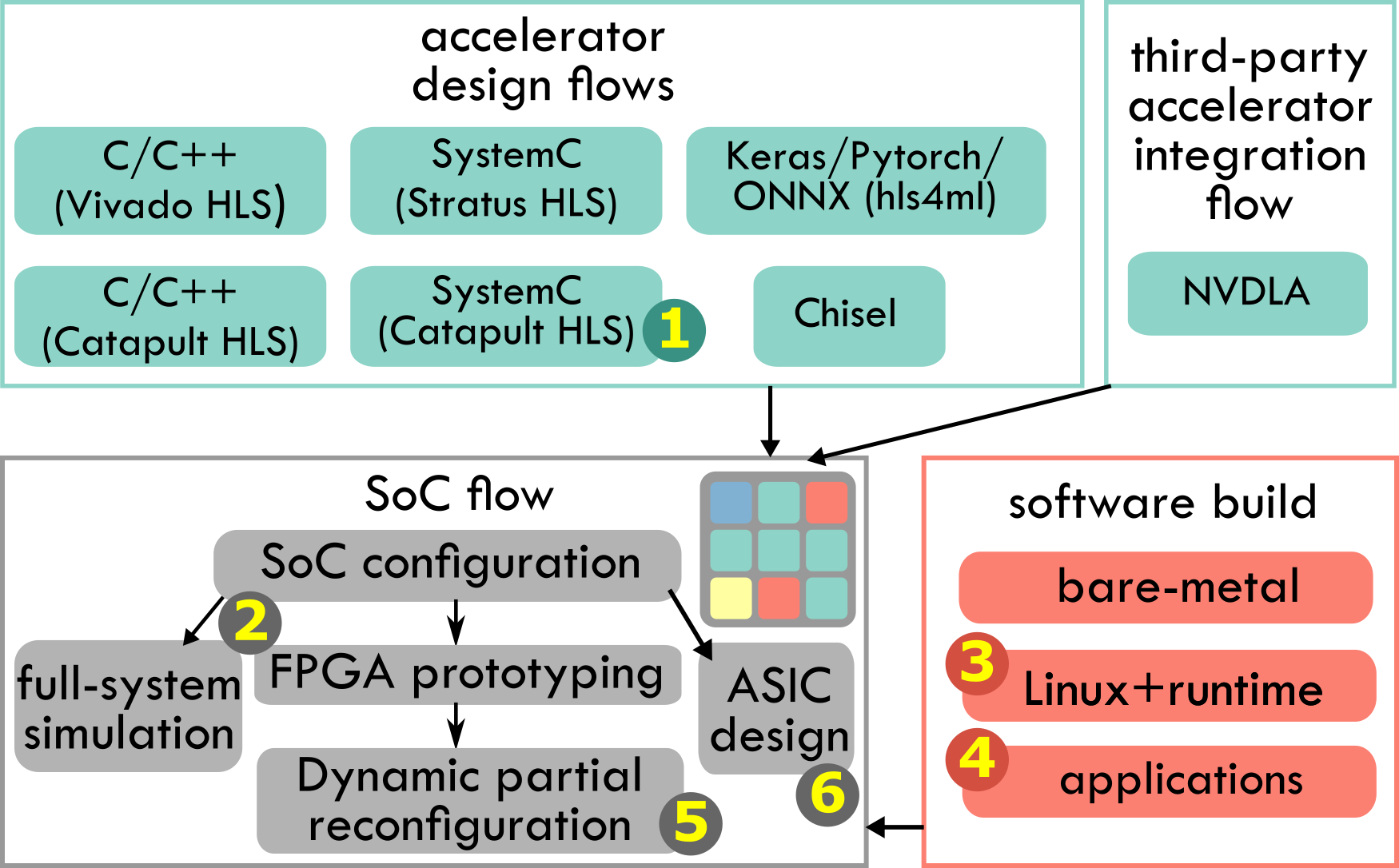

This tutorial illustrates ESP, an open-source platform that supports research on the design and programming of heterogeneous SoC architectures. By combining a scalable modular architecture with a system-level design methodology, ESP simplifies the design of individual accelerators and automates their hardware/software integration into complete SoCs. ESP provides flows for realizing these SoCs both as FPGA prototypes and, more recently, real ASIC implementations. This tutorial will focus on recent developments to ESP that enhance its methodology. First, we will showcase how to design a new accelerator in SystemC, leveraging the commercial Catapult HLS tool with the open-source Matchlib library. Next, we will demonstrate new dynamic partial reconfiguration capabilities of FPGA-based ESP implementations that allow for swapping accelerator implementations at runtime. Finally, we will describe the design flow that enabled the first ASIC implementations of ESP and demonstrate how to integrate a technology available in an open-source process design kit into ESP-based chip designs.

For more information check out the Github release, the Publications page and the Tutorials and talks page on this website.

Preliminary setup

If they wish, participants have the opportunity to try the parts of the tutorial that don’t require licensed CAD tools or FPGAs. Doing so requires to go through some preliminary setup before the beginning of the tutorial. There are two options:

-

use the Docker image for the ESP tutorial: instructions.

-

install on your machine the packages and tools required by ESP: instructions.

Program

The tutorial starts with a complete overview of the ESP project followed by a series of “How to” and “Demo” sections. The “How to” sections are offered in the form of a live tutorial.

Although this is a live event, in the table below we also provide links to the tutorial material for offline exploration. Some material is currently under development and will be added before the date of the tutorial. The tutorial covers many of the main components of the ESP methodology as represented in the chart below.

| Time | Agenda | Material |

|---|---|---|

| 9:00-9:25 am | Overview | Slides Video |

| 9:25-9:50 am | How to: design and integrate SystemC accelerators (Catapult HLS) ① | Tutorial |

| 9:50-10:10 am | How to: design and test a many-accelerator multi-core SoC ② | Tutorial (single-core) Tutorial (multi-core) Tutorial (many-accelerator) |

| 10:10-10:25 am | Demo: Performance analysis of accelerators using point-to-point communication ③ | Paper Slides |

| 10:25-10:40 am | Break | |

| 10:40-10:55 am | Case Study: ESP for real-time brain computer interfaces ④ | Paper Slides |

| 10:55-11:20 am | How to: design and program partially reconfigurable SoCs in ESP ⑤ | Paper |

| 11:20-11:55 am | How to: prepare an SoC for ASIC design with the Skywater PDK ⑥ | ESP’s First Chip! ASIC Methodology |

| 11:55-12:00 am | Teaching with ESP and concluding remarks | Paper Material |

Video recording

(COMING SOON!)

Team

System-Level Design (SLD) group at Columbia University, New York.

Speakers

Luca P. Carloni is professor and chair of Computer Science at Columbia University in the City of New York. He holds a Laurea Degree Summa cum Laude in Electronics Engineering from the University of Bologna, Italy, and the MS and PhD degrees in Electrical Engineering and Computer Sciences from the University of California, Berkeley. His research interests include heterogeneous computing, system-on-chip platforms, embedded systems,and open-source hardware. He coauthored over one hundred and seventy refereed papers. Luca received the NSF CAREER Award, the Alfred P. Sloan Research Fellowship, and the ONR Young Investigator Award. He is an IEEE Fellow.

Maico Cassel dos Santos is pursuing PhD in Computer Science at Columbia University. He received the M.S. degree in Microelectronics (2015) and B.S.E.E. degree (2008) from Federal University of Rio Grande do Sul (UFRGS). Previously, from 2013 to 2019, he joined a Brazilian state-owned company, where he designed security chips and IP components in addition to leading the RTL team to establish its design flow. From 2008 to 2013, he worked in the IC-Brazil program, a Brazilian government program in partnership with Cadence Design Systems for the first three years, where he trained hundreds of Brazilian engineers in Cadence’s digital tools.

Kuan-Lin Chiu is a PhD student in Computer Science at Columbia University. He received his BS degree in Engineering Science and Ocean Engineering from National Taiwan University and MS degree in Electrical and Computer Engineering from University of California, Los Angeles. His research interests include system-level design methodologies for heterogeneous system-on-chip platforms, focusing on hardware accelerators and on-chip data movement for image processing and machine learning.

Guy Eichler is a Computer Science PhD candidate at Columbia University in the city of New York. He holds the MS and MPhil degrees in Computer Science from Columbia University, and BS in Electrical Engineering from Technion – Israel Institute of Technology. He worked for several years at IBM as a Design Verification Engineer. He served in the Israeli Defense Forces (IDF) and obtained the rank of staff sergeant as a Special Intelligence Team Leader. His research interests include systems for Brain-Computer Interfaces (BCI), heterogeneous systems-on-chip, hardware accelerators, and computation in constrained environments. He is currently involved in multiple projects for implant-based BCI for signal resolution and data transfer between the brain and the digital world.

Biruk Seyoum received his Ph.D from the Real-Time Systems (ReTiS) Laboratory of Scuola Superiore Sant’Anna. He graduated in Electrical and Computer Engineering from Addis Ababa Institute of Technology and received M.S degree in Telecommunication and Electronics from the University of Trento in Italy. His research interests include design and implementation of heterogeneous architectures for reconfigurable platforms, design tools and applications for dynamic partially reconfigurable platforms, and FPGA-based deep neural networks acceleration. He is currently a post-doctoral research scientist at the system-level-design group at Columbia university.

Gabriele Tombesi is a PhD student in Computer Science at Columbia University. He received the joint M.S. degree in Electrical Engineering from the Politecnico di Torino, École Polytechnique Fédérale de Lausanne and Grenoble INP and the B.S. degree in Physical Engineering from the Politecnico di Torino. His research interests include HLS-based design flows for hardware acceleration of Deep Learning workloads and Design for Testability techniques for heterogeneous system-on-chip architectures.

Joseph Zuckerman is a Computer Science PhD candidate at Columbia University. His research focuses on agile design methodologies, novel architectures, and runtime optimization of heterogeneous systems-on-chip. He is the recipient of a NSF graduate research fellowship. Joseph previously completed his bachelor’s degree in Electrical Engineering from Harvard University in 2019 and his master’s degree in Computer Science from Columbia University in 2021. He currently leads the development of ESP.