DATE 2023 tutorial

Design, Programming, and Partial Reconfiguration of Heterogeneous SoCs with ESP

Latest update: 2023-04-17

Logistics

Tutorial date: Wednesday, April 19,2023.

Tutorial venue: Flanders Meeting & Convention Center Antwerp (Toucan Room 2.7.1/2 (2nd floor)).

Tutorial registration: Registration instructions.

Preliminary setup: Instructions.

Hands-on tutorial steps: (COMING SOON!)

If you are interested in attending this tutorial, please be sure to sign up for it when registering for ASPLOS.

What is ESP?

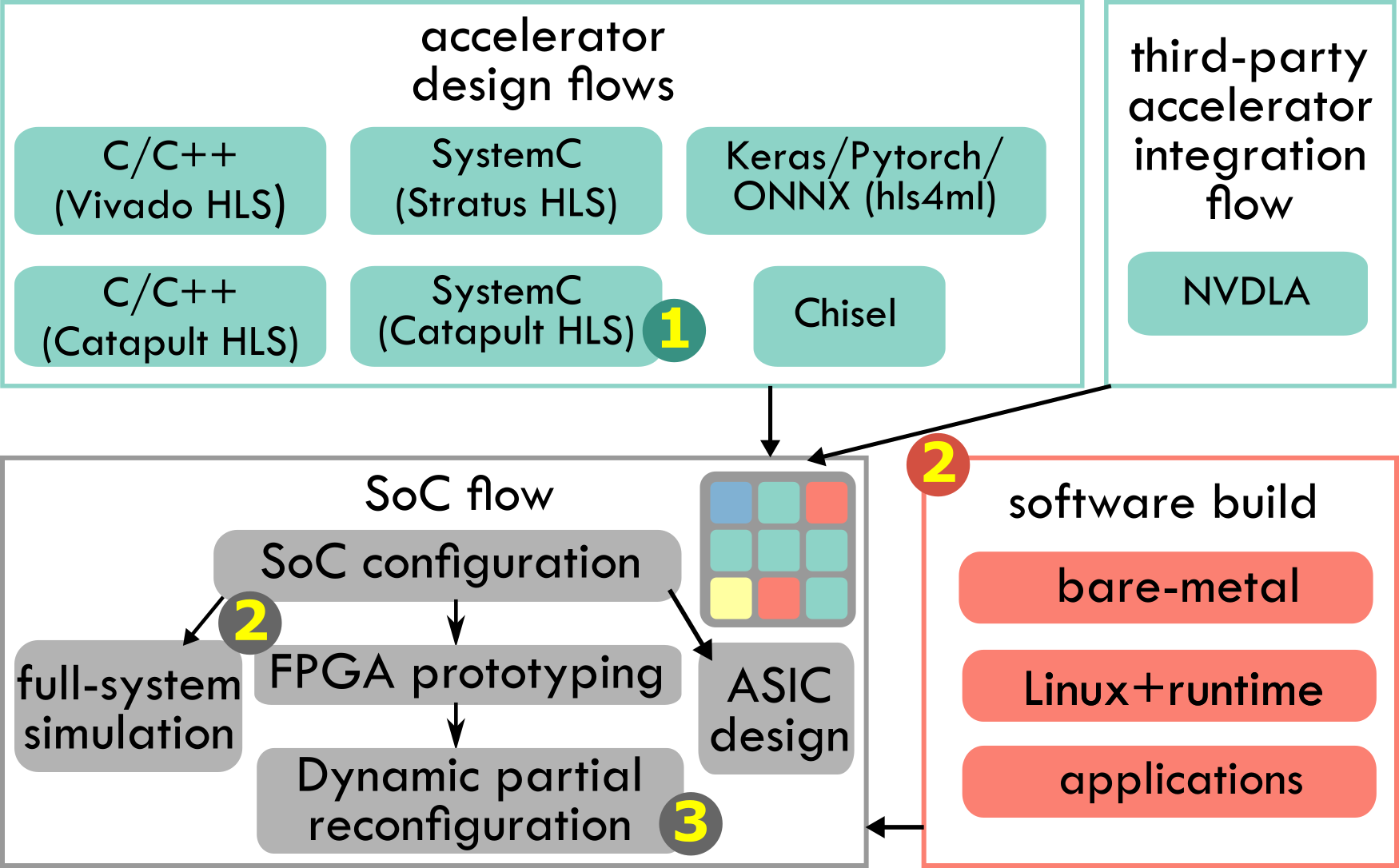

Energy-efficient, high-performance computing requires the integration of specialized accelerators with general-purpose processors. Designing such systems, however, imposes a difficult set of challenges: integrating many components of different natures into a single SoC; designing new components targeting a particular application domain with a limited team size; dealing with ever-changing software; accelerating multiple applications with a fixed area and power budget. In this tutorial, we present ESP, an open-source platform to support research on the design and programming of heterogeneous SoC architectures. By combining a scalable, modular tile-based architecture with a flexible system-level design methodology, ESP simplifies the design of individual accelerators and automates their hardware/software integration into complete SoCs. In particular, we demonstrate several capabilities of ESP to meet the challenges described above. First, we show how to use the commercial Catapult HLS tool and the open-source Matchlib library to design an accelerator in SystemC; this is a new example of one of the design flows supported by the ESP methodology that simultaneously raise the level of abstraction in the design process and allow designers to conduct a broader design-space exploration. Next, we demonstrate how ESP simplifies the integration of the accelerator into a complete SoC and enables its functional and performance evaluation through rapid FPGA-based prototyping. Finally, we show how recent advances in ESP make it possible to reduce the amount of dark silicon in SOC architectures through fine-grained partial reconfiguration of accelerator tiles.

For more information check out the Github release, the Publications page and the Tutorials and talks page on this website.

Preliminary setup

If they wish, participants have the opportunity to try the parts of the tutorial that don’t require licensed CAD tools or FPGAs. Doing so requires to go through some preliminary setup before the beginning of the tutorial. There are two options:

-

use the Docker image for the ESP tutorial: instructions.

-

install on your machine the packages and tools required by ESP: instructions.

Program

The tutorial starts with a complete overview of the ESP project followed by a series of “How to” and “Demo” sections. The “How to” sections are offered in the form of a live tutorial.

Although this is a live event, in the table below we also provide links to the tutorial material for offline exploration. Some material is currently under development and will be added before the date of the tutorial. The tutorial covers many of the main components of the ESP methodology as represented in the chart below.

| Time | Agenda | Material |

|---|---|---|

| 15min | Overview | Slides Video |

| 25min | How to: design and integrate SystemC accelerators (Catapult HLS) ① | Tutorial |

| 25min | How to: design and program a many-accelerator multi-core SoC ② | Tutorial (single-core) Tutorial (multi-core) Tutorial (many-accelerator) |

| 25min | How to: apply dynamic partial reconfiguration to accelerator tiles ③ | Paper |

Video recording

(COMING SOON!)

Team

System-Level Design (SLD) group at Columbia University, New York.

Speakers

Luca P. Carloni is professor and chair of Computer Science at Columbia University in the City of New York. He holds a Laurea Degree Summa cum Laude in Electronics Engineering from the University of Bologna, Italy, and the MS and PhD degrees in Electrical Engineering and Computer Sciences from the University of California, Berkeley. His research interests include heterogeneous computing, system-on-chip platforms, embedded systems,and open-source hardware. He coauthored over one hundred and seventy refereed papers. Luca received the NSF CAREER Award, the Alfred P. Sloan Research Fellowship, and the ONR Young Investigator Award. He is an IEEE Fellow.

Biruk Seyoum received his Ph.D from the Real-Time Systems (ReTiS) Laboratory of Scuola Superiore Sant’Anna. He graduated in Electrical and Computer Engineering from Addis Ababa Institute of Technology and received M.S degree in Telecommunication and Electronics from the University of Trento in Italy. His research interests include design and implementation of heterogeneous architectures for reconfigurable platforms, design tools and applications for dynamic partially reconfigurable platforms, and FPGA-based deep neural networks acceleration. He is currently a post-doctoral research scientist at the system-level-design group at Columbia university.

Gabriele Tombesi is a PhD student in Computer Science at Columbia University. He received the joint M.S. degree in Electrical Engineering from the Politecnico di Torino, École Polytechnique Fédérale de Lausanne and Grenoble INP and the B.S. degree in Physical Engineering from the Politecnico di Torino. His research interests include HLS-based design flows for hardware acceleration of Deep Learning workloads and Design for Testability techniques for heterogeneous system-on-chip architectures.

Joseph Zuckerman is a Computer Science PhD candidate at Columbia University. His research focuses on agile design methodologies, novel architectures, and runtime optimization of heterogeneous systems-on-chip. He is the recipient of a NSF graduate research fellowship. Joseph previously completed his bachelor’s degree in Electrical Engineering from Harvard University in 2019 and his master’s degree in Computer Science from Columbia University in 2021. He currently leads the development of ESP.