MICRO 2020 tutorial

ESP: an Open-Source Platform for Agile SoC Development

Latest update: 2021-05-27

Logistics

Tutorial date: 1pm-4pm EDT, Saturday October 17, 2020. See here the MICRO tutorials program.

Tutorial venue: Zoom seminar on the Whova platform (link).

Tutorial registration: Registration instructions.

Preliminary setup: Instructions.

What is ESP?

The system-on-chip (SoC) lies at the core of modern computing systems for a variety of domains, from embedded systems to data centers. In any given domain, the success of a particular SoC architecture is bound to the set of special-purpose hardware accelerators that it features next to general-purpose processors. This heterogeneity of SoC components brings new challenges to hardware designers as well as software programmers.

This tutorial illustrates ESP, a new open-source platform to support research on the design and programming of heterogeneous SoC architectures. By combining a scalable modular architecture with a system-level design methodology, ESP simplifies the design of individual accelerators and automates their hardware/software integration into complete SoCs. Furthermore, ESP enables rapid prototyping of these architectures on FPGA-based infrastructures. With ESP, researchers in architectures, compilers, and operating systems can evaluate new ideas by running complex user applications on top of a complete Linux-based software stack and invoke many different hardware accelerators to process very large data sets from main memory.

For more information check out the Github release, the Publications page and the Tutorials and talks page on this website.

Preliminary setup

If they wish, participants have the opportunity to try the parts of the tutorial that don’t require licensed CAD tools or FPGAs. Doing so requires to go through some preliminary setup before the beginning of the tutorial. There are two options:

- use the Docker image for the ESP tutorial: instructions.

- install on your machine the packages and tools required by ESP: instructions.

Program

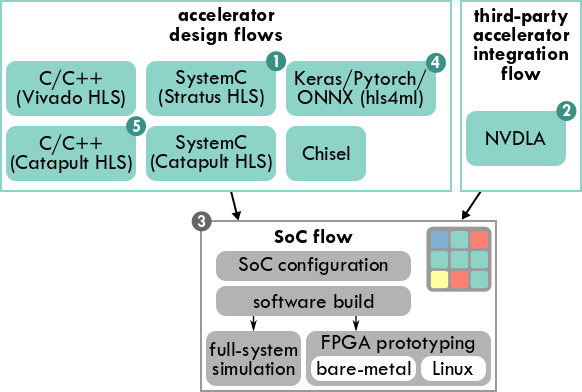

The tutorial starts with a complete overview of the ESP project followed by a series of “How to” and “Demo” sections. The “How to” sections are offered in the form of a live tutorial over Zoom. Although this is a live virtual event, in the table below we also provide links to the tutorial material for offline fruition. The tutorial covers many of the main components of the ESP methodology as represented in the chart below.

| Time | Agenda | Material |

|---|---|---|

| 45min | Overview - heterogeneous SoC architecture - accelerator design and integration flows - accelerator programming - SoC design flow - simulation and FPGA prototyping - teaching - project status |

Slides Video |

| 30min | How to: design and integrate SystemC accelerators (Stratus HLS) ① | Tutorial |

| 15min | How to: integrate third-party accelerators (NVDLA) ② | Tutorial |

| 30min | How to: design and test a many-accelerator multi-core SoC ③ | Tutorial (single-core) Tutorial (multi-core) Tutorial (many-accelerator) |

| 15min | How to: design and integrate Keras/Pytorch/ONNX accelerators ④ | Tutorial |

| 30min | How to: design and integrate C/C++ accelerators (Catapult HLS) ⑤ | Tutorial |

| 15min | Demo: reconfigurable cache-coherence for accelerators | Demo |

Video recording

Video recording of the live tutorial:

Team

System-Level Design (SLD) group at Columbia University, New York.

Speakers

Luca P. Carloni is Professor of Computer Science at Columbia University in the City of New York. He holds a Laurea Degree in Electronics Engineering from the University of Bologna and the MS and PhD degrees in Electrical Engineering and Computer Sciences from UC Berkeley. His research interests are in system-on-chip platforms and distributed embedded systems. He coauthored over one hundred and forty refereed papers. Luca received the NSF CAREER Award, the ONR Young Investigator Award, and an Alfred P. Sloan Research Fellowship. In 2013, Luca served as general chair of Embedded Systems Week. Luca is an IEEE Fellow.

Giuseppe Di Guglielmo is an Associate Research Scientist with the Department of Computer Science, Columbia University, New York. Giuseppe received the Laurea degree and the PhD degree in Computer Science from the University of Verona, Italy. His PhD thesis was on the verification and validation of system-level hardware design. His current research topics include the design, validation, and security of hardware accelerators. He is also interested in the acceleration of machine learning applications for physics and robotics with high-level synthesis and FPGA platforms. He has authored over 70 publications.

Davide Giri is a PhD student in Computer Science at Columbia University. He received the MS degree in electronic engineering from Politecnico di Torino and the MS degree in electrical and computer engineering from the University of Illinois at Chicago. His research interests include architectures and system-level design methodologies for heterogeneous system-on- chip, with particular focus on hardware accelerators and on-chip data movement. Davide is one of the main architects of the ESP project.

Paolo Mantovani is an Associate Research Scientist at Columbia University. He earned the MS in Electronic Engineering at Politecnico di Torino and the PhD in Computer Science at Columbia University. His PhD and current research interests include architecture design and system-level methodologies for the integration and programming of heterogeneous computing platforms. Paolo contributes to the open-source hardware community as the main architect of the ESP architecture and FPGA emulation infrastructure.